一款串行 (UART/SPI) - USB 2.0 Host/Device LSI

UART 连接(异步串行 I/F)

SPI 连接(时钟同步串行 I/F)

内置USB稳压器

内置VBUS供电功能

S1R72U06:一款串行 (UART/SPI) - USB 2.0 Host/Device LSI

完整型号:

S1R72U06F12E100

S1R72U06F07E100

S1R72U06概述

S1R72U06 是一款串行 (UART/SPI) - USB 2.0 Host/Device LSI,支持 USB 2.0 FS/LS。主 CPU 使用简化命令控制 LSI 的 USB 功能。无需 USB 驱动程序。支持的 USB 类是大容量存储类(用于 USB 主机操作)和人机接口设备类(用于 USB 主机/设备操作)。

S1R72U06特征

l 易于使用和易于连接(串行连接)

使用简化的命令来控制 USB 功能

主 CPU 使用简化命令控制该 LSI 的 USB 功能。无需安装 USB 驱动程序。

UART(2 线异步)或 SPI(时钟同步)串行接口允许轻松连接各种 CPU 类型。

l 内置稳压器

USB 稳压器

核心电压调节器

S1R72U06 有两个稳压器:一个(输入范围:3.3 至 5.0 V)为 USB 生成 3.3 V,另一个(输入电压:3.3 至 5.0 V)生成 1.8 V 的内部核心电压。这允许 S1R72U06 运行只要提供的电压至少为 3.3 V,就可以使用单个电源。

l 内置VBUS供电功能

无需外部 VBUS 电源 SW

S1R72U06 具有用于 USB 主机操作的内置 VBUS 电源功能,无需 USB 主机控制器之前需要的外部 VBUS 电源 SW。如果内置 VBUS 供电功能无法提供足够的电流,S1R72U06 具有一个接口,可以控制外部 VBUS 电源 SW。如有必要,连接外部 VBUS 电源 SW 以确保总线供电设备有足够的电流容量。

l 产品(系统)开发支持功能

历史显示

S1R72U06使用串行接口(异步型)来显示内部LSI处理的历史等。该功能在产品(系统)开发过程中提供有用的信息。

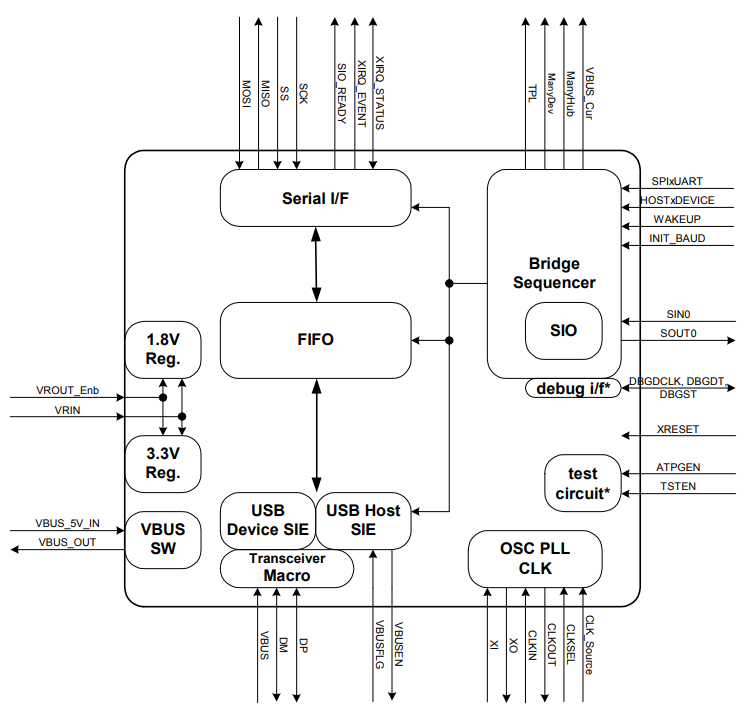

S1R72U06系统框图

S1R72U06功能

串行接口(UART/SPI)

S1R72U06 通过 UART(2 线异步)或 SPI(时钟同步)连接到主 CPU。与 UART 一起使用时,将 SPIxUART 模式设置引脚设置为低电平。与 SPI 一起使用时,将 SPIxUART 模式设置引脚设置为高电平。

接口电压 (CVDD) 的使用范围很广,从 1.8 到 5.0 V。

• UART 连接(异步串行 I/F)

初始波特率:300/9600 bps(由模式设置引脚 INIT_BAUD 设置)

波特率:可设置(最大 3 Mbps)

lsb优先

8位数据

1/2 停止位

奇/偶/无奇偶校验

• SPI 连接(时钟同步串行 I/F)

SPI从机

模式 0(正脉冲锁存优先)

波特率:最大。 6 Mbps(SCK 引脚输入)

msb优先

8位数据

USB 主机 SIE

USB 主机功能符合 USB 2.0(通用串行总线规范修订版 2.0)标准。它支持 FS (12 Mbps) 和 LS (1.5 Mbps) 速度模式。 USB 功能由 Bridge 控制

LSI 内部的定序器块。支持的 USB 类是大容量存储类和人机界面设备类。

USB 设备 SIE

USB 设备功能符合 USB 2.0(通用串行总线规范修订版 2.0)标准。

它支持 FS (12 Mbps) 和 LS (1.5 Mbps) 速度模式。 USB 功能由 Bridge 控制LSI 内部的定序器块。支持的 USB 类是人机接口设备类。

收发宏

这是主机和设备共享的 USB 模拟宏块。

先进先出FIFO

该 FIFO 块用作串行接口和 USB 之间的数据缓冲区。

桥序器

它根据来自串行接口的命令控制 USB 功能。

SIO

此块用于显示产品(系统)开发支持功能的历史记录和模拟测试。

调试接口

这是内置桥接定序器的调试引脚。它不是供用户使用的,应该是无视。

1.8V稳压器

该稳压器产生 1.8V 的内部内核电压。输入电压范围为 3.3 至 5.0 V。

3.3V稳压器

该稳压器为 USB 生成 3.3 V。输入电压范围为 3.3 至 5.0 V。

VBUS 软件

这是 LSI 中内置的 VBUS 输出模块。

测试电路

这是用于IC测试的电路。它不是供用户使用的,应该被忽略。

S1R72U06封装

Product Number | Package |

S1R72U06F12E100 | QFP12-48 package |

S1R72U06F07E100 | QFN7-48 package |

在线咨询

在线咨询