汽车级桥接IC

SPI 连接(16 字节缓存的校验和功能)

输入像素时钟/同步,信号监测

CRC(全屏/寄存器设置/帧比较)

输出水印功能

黑屏

错误/中断引脚

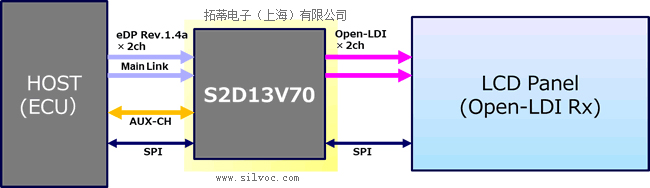

S2D13V70:爱普生(EPSON) Golden Gate汽车级桥接IC (eDP⇒OpenLDI Bridge IC)

S2D13V70是一款eDP(rev.1.4a) to Open LDI桥接设备,可以实现eDP源到具有Open LDI接口的显示面板之间的连接。它可以通过1 lane/2lane eDP接收1.62Gbps/2.7Gbps的数据速率,并将其转换为具有2ch Open LDI信号的传输,像素时钟频率高达148.5MHz(每1ch)。

该规范非常简单,因此可以轻松插入现有系统显示架构,只需进行很小的修改,使其成为现有和未来设计的理想解决方案。

S2D13V70还通过了包括AEC-Q100认证和多项功能安全特性在内的汽车设计认证。

S2D13V70的eDP Rx IP (rev1.4a)也可以连接到DP (rev1.3和1.4)信号。

S2D13V70特征

型号 | 简易桥S2D13V70 |

供电电压 | 3.3V / 1.8V dual supply |

输入 | eDP rev.1.4a x 2Lane, Max 2.7Gbps/lane |

输出 | OpenLDI-Tx x 2Ch, Max120MHz/ch |

显示分辨率 | up to 1920 x 1200@60fps |

主接口 | SPI |

图像校正 | 8-bit Digital Gamma LUT + 2-bit Dithering |

安全特性 | SPI connection (checksum function by 16byte cache) |

Input pixel clock/sync. signal monitoring | |

CRC (Full screen / Register setting / Frame comparison) | |

Output watermark function | |

Blank screen | |

Error / Interrupt pins | |

汽车标准 | AEC-Q100 qualifications |

Ta : -40 ~ 105℃ | |

其他 | System Clock : 48MHz for always running clock |

SPI Bridge (SPI Slave to Master bridge) | |

Splitter function (Line split / LR split) | |

封装 | PFBGA8-81 (8mm x 8mm x 1.2mm, 0.8mm pitch) |

开发状态 | 正在开发中Under Development |

S2D13V70系统框图

S2D13V70拆分器功能

拆分器功能(线或LR拆分)

分辨率大小:可以在1920×1080分辨率内进行双屏显示。

在线咨询

在线咨询