可编程压控晶振(VCXO);频率范围:50 MHz to 800 MHz (调谐分辨率: 2.2 to 2.8 x 10-9)

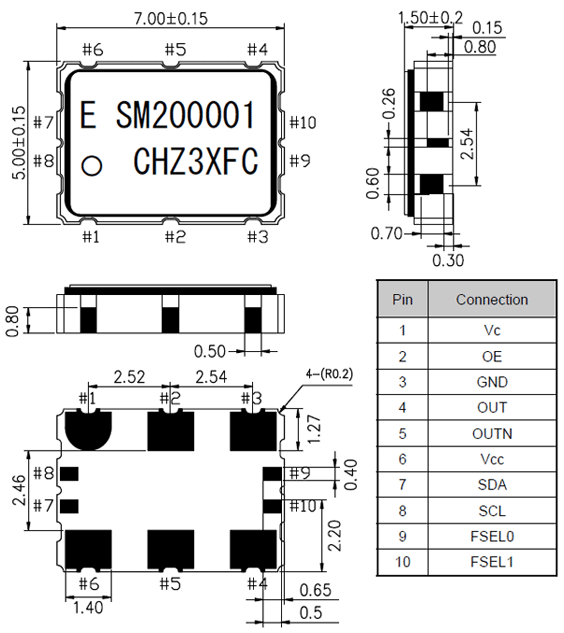

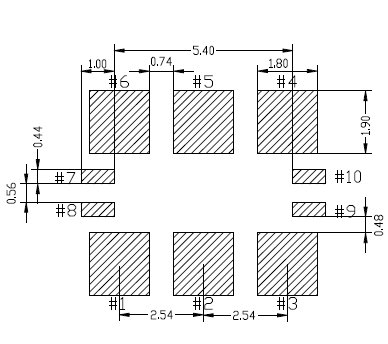

电源电压:2.5 V / 3.3 V;外部尺寸:7.0 × 5.0 × 1.5 mm (10pins)

绝对频率控制范围:±0 to ±180 x 10-6(12steps selectable)

特征:用户指定的一个启动频率;APR和7位I2C地址;用户编程:I2C接口;低抖动PLL技术

应用领域:SONET/SDH, OTN, GbE, 光纤通道(Fibre Channel)

VG7050ECN:爱普生 (EPSON) 可编程压控晶振、晶体振荡器(VCXO)输出:LV-PECL

VG7050ECN常用频率列表如下:

规格型号 | 产品编码 | MOQ (PCS) |

VG7050ECN | X1G004561xxxx00 | 1000 |

VG7050ECN SM200005 DJGLPZ | X1G004561000500 | 1000 |

VG7050ECN 50.000000MHz SM20xxxx CJGHPZ | X1G004561xxxx00 | 1000 |

VG7050ECN 125.000000MHz SM20xxxx CJGHPZ | X1G004561xxxx00 | 1000 |

VG7050ECN 156.250000MHz SM20xxxx CJGHPZ | X1G004561xxxx00 | 1000 |

VG7050ECN 250.000000MHz SM20xxxx CJGHPZ | X1G004561xxxx00 | 1000 |

VG7050ECN 425.000000MHz SM20xxxx CJGHPZ | X1G004561xxxx00 | 1000 |

VG7050ECN 622.080000MHz SM20xxxx CJGHPZ | X1G004561xxxx00 | 1000 |

VG7050ECN 669.330000MHz SM20xxxx CJGHPZ | X1G004561xxxx00 | 1000 |

VG7050ECN 794.730000MHz SM20xxxx CJGHPZ | X1G004561xxxx00 | 1000 |

爱普生(EPSON)可编程压控晶振: VG7050ECN

· 频率范围:

50 MHz to 800 MHz (调谐分辨率: 2.2 to 2.8 x 10-9)

· 电源电压:

2.5 V / 3.3 V

· 外部尺寸:

7.0 × 5.0 × 1.5 mm (10pins)

· 绝对频率控制范围(频率控制范围-频率容差):

±0 to ±180 x 10-6(12steps selectable)

· 特征:

用户指定的一个启动频率

APR和7位I2C地址

用户编程:I2C接口

低抖动PLL技术

· 应用领域:

SONET/SDH, OTN, GbE, 光纤通道(Fibre Channel)

· 光同步数字传输网 (SONET/SDH: Synchronous Optical Network / Synchronous Digital Hierarchy)

· 光传送网 (OTN: Optical Transport Network)

· 千兆以太网 (GbE)

· 光纤通道 (Fibre Channel)

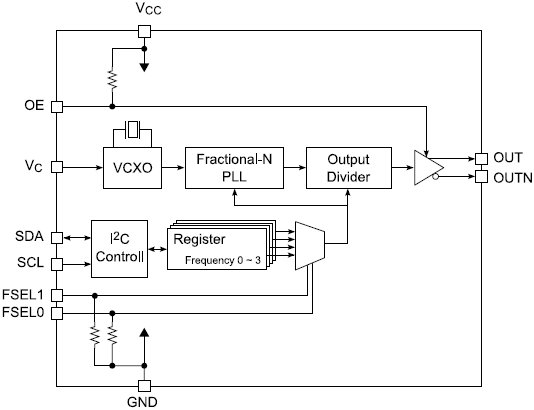

可编程压控晶振:VG7050ECN是一种低抖动的在任意频率下可编程的VCXO。 VG7050ECN由VCXO、PLL和LVPECL输出缓冲器组成。其输出频率可从50 MHz编程到800 MHz,分辨率几乎为2 ppb。

VCXO为PLL提供稳定的基准时钟,并带有基频晶体。VCXO的Kv可通过I2C接口编程。

PLL由低抖动分-N PLL技术组成。环路滤波器的组件嵌入到IC中,因此不需要外部组件。

• 可编程时钟输出频率从50 MHz到800 MHz

• 频率设置分辨率约为2 ppb

• Kv可编程

• 来自基频内部晶体的低抖动和高可靠性时钟源

• 低抖动和低噪声PLL

• 一个加电默认频率

• 出厂预设设备选项

OE极性

输出待机类型:Hi-Z或OUT=“L”,OUTN=“H”

I2C接口从属地址

• 用于振荡器的嵌入式电阻和电容以及用于PLL的环路滤波器

• I2C接口

• LV-PECL输出

• 8针陶瓷5×7 mm封装

• 2.5V或3.3V电源电压模式

• -40°C to +85°C环境工作温度

• 无铅/符合RoHS

规格 (特征)

项目 | 符号 | 规格说明 | 条件 / 备注 |

输出频率范围 | f0 | 50 MHz to 800 MHz | It can be changed by I2C |

电源电压 | VCC | D:2.5V ±0.125V | |

储存温度 | T_stg | -55°C to +125°C | Store as bare product after packing |

工作温度 | T_use | G:-40°C to +85°C | |

频率稳定度 *1 | f_tol | J: ± 50 × 10-6 Max | Includes frequency aging (10 years) |

功耗 | ICC | 90 mA Max. | OE Active, |

禁用电流 | I_dis | 40mA Max. | OE Inactive, Output Standby: Hi-Z mode |

70mA Max. | OE Inactive, Output Standby: Fix mode | ||

绝对频率控制范围 | APR | ±0~±180 x 10-6 | Vc = 1.65 V ± 1.35 V |

±0~±180 x 10-6 | Vc = 1.25 V ± 1.00 V | ||

控制电压调谐范围 | Vc | 0~Vcc | |

频率变化极性 | - | Positive slope | |

占空比 | SYM | 45% ~ 55% | At outputs crossing point |

输出电压 | VOH | VCC -1.025 V Min. | DC characteristics |

VOL | VCC -1.62 V Max. | ||

输出负载条件 | L_ECL | 50Ω | Termination to VCC-2.0V |

输入电压 | VIH | 70% VCC Min. | OE,SDA, and SCL |

VIL | 30% VCC Max. | ||

上升/下降时间 | tr / tf | 400 ps Max. | Between20% to 80% of (VOH- VOL) |

启动时间 | t_str | 10 ms Max. | Time at minimum supply voltage to be 0 s |

绝对频率控制范围=频率控制范围-频率公差。

*1. 频率公差包括初始频率公差、温度变化、电源电压变化、回流漂移和10年老化(+25°C,10年)。

VG7050ECN等系列晶振产品名称参数:

(1) 产品名称 (标准形式)

VG7050EAN SM18xxxx C J G H P Z

VG7050ECN SM20xxxx C J G H P Z

① ② ③ ④⑤⑥⑦⑧⑨

① Model

② Output (E: LV-PECL)

③ Parameter Designator ( EAN : SM18xxxx, ECN : SM20xxxx )

④ Supply voltage (C: 3.3 V Typ., D: 2.5 V Typ.)

⑤ Frequency tolerance (J: ±50 × 10-6)

⑥ Operating temperature (G: -40 ~ +85°C)

⑦ OE Function (H: Active High, L: Active Low)

⑧ Absolute Pull Range (P: Programmable)

⑨ Output Standby Type (F: Fix (OUT=”L”, OUTN=”H”), Z: High-Z)

(2) 产品型号 / 产品编码 (空白部分由每个详细规范决定。)

VG7050EAN X1G004541xxxx00

VG7050ECN X1G004561xxxx00

① ② ③ ④ ⑤

① Crystal devices ② Model ③ Pb free code(1:EU RoHS / Pb free)

④ Detail specifications

⑤ Packing(00:Standard packing)

相位抖动

Offset Frequency | 125.00 MHz | 156.25 MHz | 250.00 MHz | 425.00 MHz | 622.08 MHz | 669.33 MHz | 794.73 MHz | |

相位抖动*2 | 12 kHz to 20 MHz | 0.30 ps | 0.26 ps | 0.26 ps | 0.25 ps | 0.26 ps | 0.26 ps | 0.26 ps |

20 kHz to 50 MHz | 0.30 ps | 0.27 ps | 0.27 ps | 0.26 ps | 0.27 ps | 0.27 ps | 0.27 ps | |

50 kHz to 80 MHz | 0.29 ps | 0.27 ps | 0.27 ps | 0.26 ps | 0.27 ps | 0.27 ps | 0.27 ps |

*2. 为了实现较佳抖动性能,建议VCC-GND引脚之间的电容(0.1µF+10µF)应尽可能靠近VCC引脚。

电路框图

*如果OE引脚配置为低电平,则OE引脚通过内部下拉电阻下拉至GND。

OE 功能 / OE 待机类型

OE Function | OE Standby Type | Frequency output | Oscillator Stop | |

OE pin | OUT, | |||

H:Active High | Z: High-Z | "H" or "OPEN" | "L" | High Impedance |

L:Active Low | "L" or "OPEN" | "H" | ||

H:Active High | L | "H" or "OPEN" | "L" | OUT="L", OUTN="H" |

L:Active Low | "L" or "OPEN" | "H" | ||

为了实现较佳的抖动性能,建议VCC和GND引脚之间的电容(0.1µF+10µF)应尽可能靠近VCC引脚。

在线咨询

在线咨询